写在前面的话

静态时序分析(Static Timing Analysis),缩写为STA。是对数字IC电路的检查验证,注意,这里不是检查电路的功能。而是检查所有时序路径是否满足,就是检查所有触发器是否满足建立时间和保持时间。静态指的是,没有输入激励,只是对所有时序路径进行检查,分析速度快。

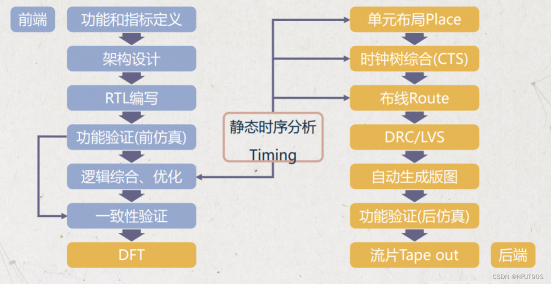

由于静态时序分析是对时序路径进行检查,在数字IC设计流程中,从综合开始,直到布局布线结束,每对实际的电路和器件进行修改,都需要重新跑一次静态时序分析,确保电路在时序上是正确的。因此,STA是前端和后端的关键连接点,对应的岗位也是非常重要的,STA算是数字IC设计中需求最大、经验要求高的一个岗位方向。

对于在校学生,如果研究方向不是时序分析相关的同学,对STA的掌握要求就是了解基础知识点,会完成建立和保持时间检查,了解TCL等脚本语言在时序约束中的应用,就可以了。如果能有相关的实践经验则是最好的了。

STA在芯片设计流程中处于关键位置: (截图来源于西南交通大学,邸志雄老师的《硬件加速设计方法》,在b站上有视频,感兴趣的同学可以去看看)

我在整个笔面过程中,遇到的STA相关考点大致就是一下几类:

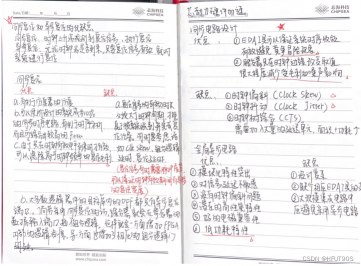

(1)时钟相关的专业术语和理解;例如同步电路、异步电路、时序路径、偏差和抖动、亚稳态等。

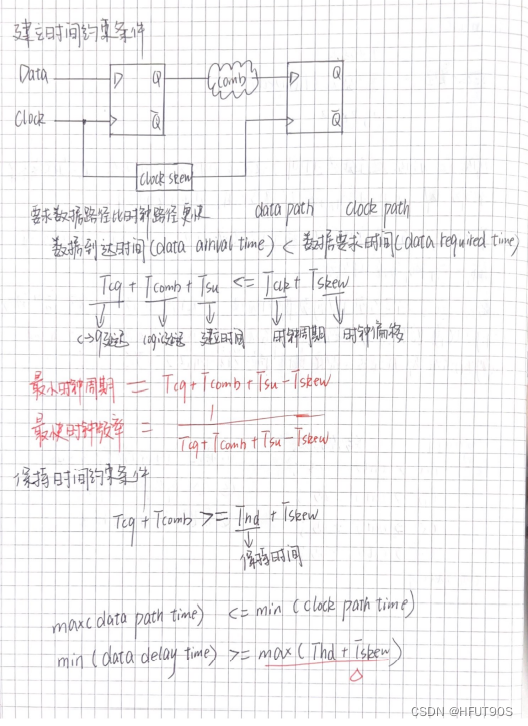

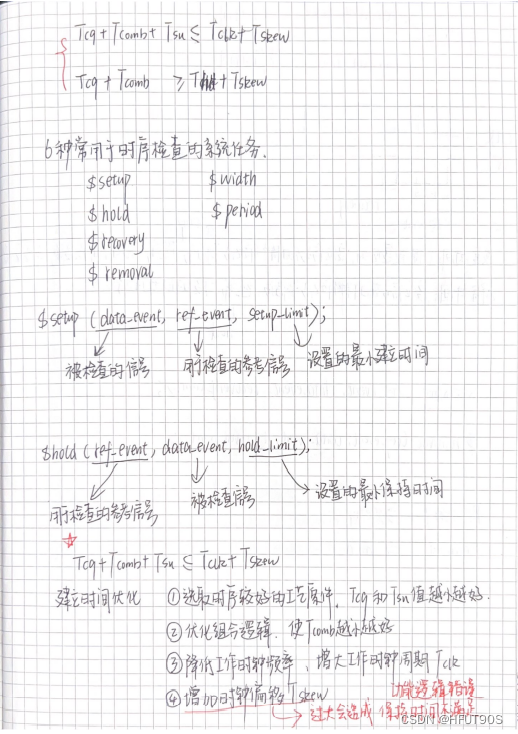

(2)建立时间和保持时间的检查,要理解两个公式的关键,理解裕量,要求时间和到达时间,关键路径等,这个是笔试最常考的知识点,两个公式一定要记好,也要有自己的理解。

(3)项目中时序分析使用的工具,脚本语言等。

(4)最难的就是时序分析的进阶知识点了,例如伪路径、多周期检查、时钟不确定,这类问题就是看你掌握的程度了,要是只会个概念理解,没有实践经验的话,对面试帮助也不大。

授人以鱼不如授人以渔(STA经典教材推荐)

我本人不是STA相关方向的研究生,对于STA的理解完全靠自学,也是一个STA的菜鸟。对于STA的理解也是在几次笔试和面试中遇见的,然后就去搜索了解STA相关的知识。这里就不班门弄斧了,先来推荐我个人遇见的,我认为不错的教材,感兴趣的同学可以购买相关的教材用来学习。

STA圣经

首要推荐的就是STA圣经,STA工程师必读教材,全书一共十章,按照自底向上的顺序编写的,整体是硬核知识点那种,我个人就是跳着看的,主要在前三章。另外知乎上有大佬翻译了整本书籍,感兴趣的同学点下面链接就可以看到。

STA圣经翻译链接: link

中文教材

中文教材推荐的就是刘峰老师编写的《集成电路静态时序分析与建模》,全书共分为11章,涉及STA关键知识,覆盖面广,另外还有TCL教程和实践举例。比较适合初学者入门学习。

软件使用教程

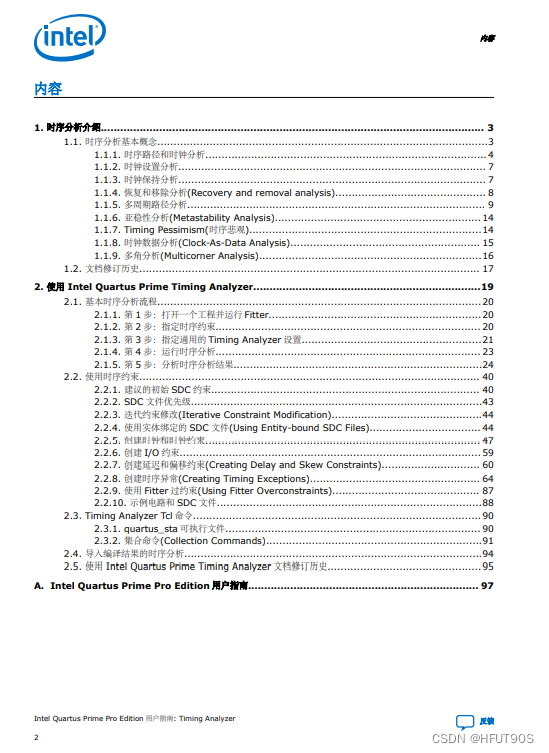

最后推荐的,就是我个人比较喜欢的一个中文教程,是Intel FPGA开发软件的使用手册,Timing Analyzer的用户指南。

一共两章,分为时序分析概念和软件教程。(在学校我是先学的Quartus 、然后学的Vivado,中间配合Modelsim和VCS、Verdi和DC等工具,Quartus是真的简单易上手。)

个人STA小结

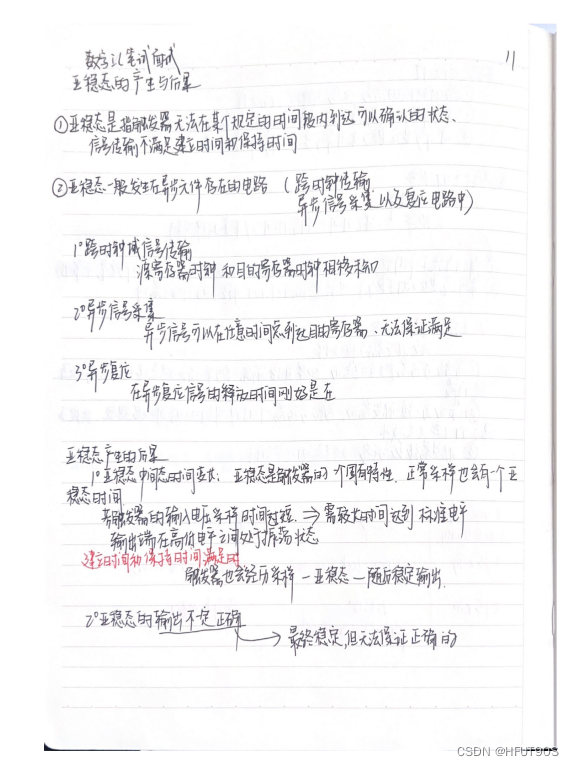

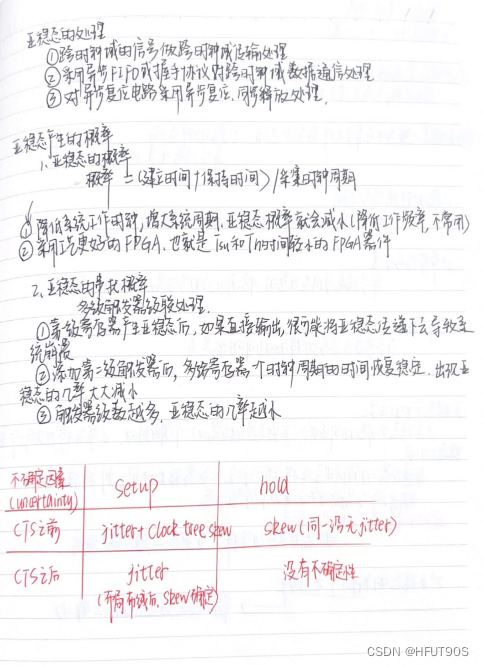

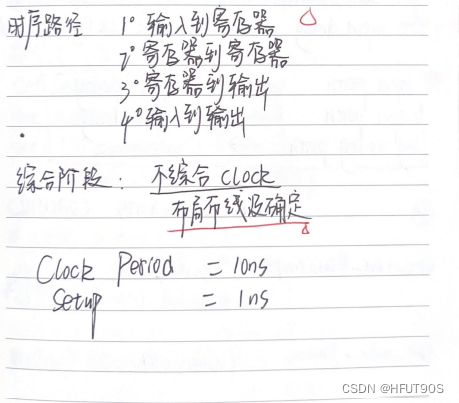

这里我就直接贴上个人写的一些笔记了,前前后后都是零散记录的,大家看看图一乐就行,我的建议是同学之间可以互相提问,然后多搜搜笔面题目,然后记录下来,有空就随手翻翻。(我是比较喜欢瞎写的,每天在笔记上写点东西总能有点收获感。虽然大部分记录的东西再回头复习的时候都感觉很简单,有的还没记录重点,但是每天都感觉自己在进步,哈哈哈哈哈哈哈)

亚稳态

建立时间、保持时间

偏差和抖动

时序路径

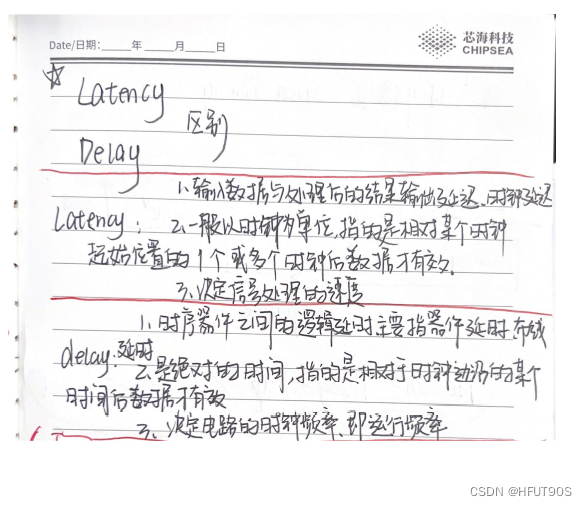

Delay和Latency

建立时间和保持时间检查

恢复时间和去除时间

同步复位和异步复位

从简单的软件开始(Time Quest使用)

列举一下Time Quest的大体流程,感兴趣的同学可以自己尝试一下。

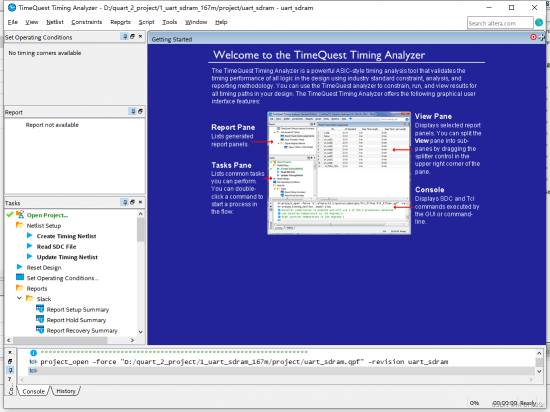

(1)在Quartus主界面,点击tools >>> TimeQuest Timing Analyzer

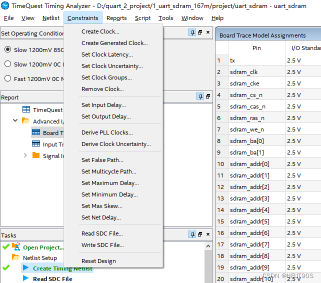

(2)点击Constraints ,这里可以设置时序分析相关的约束

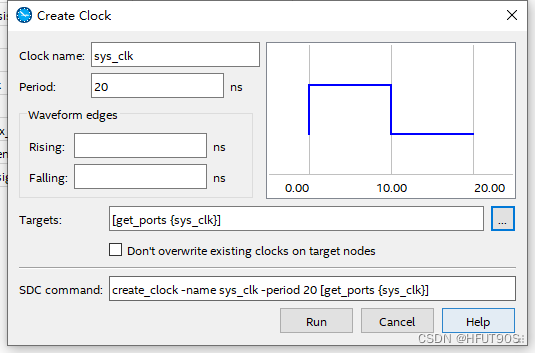

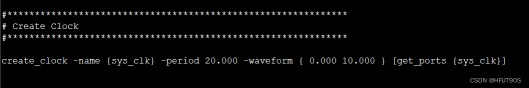

(3)这里举例,创建一个sys_clk时钟,约束到指定ports,然后点击run

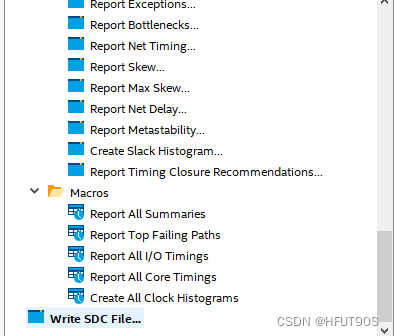

(4)再点击write SDC file ,输出约束文件,可以在约束文件中找到对应的约束脚本

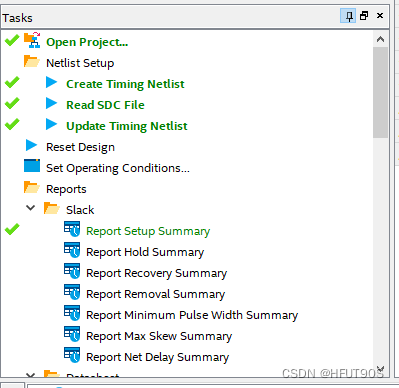

(5)再按照task窗口顺序执行

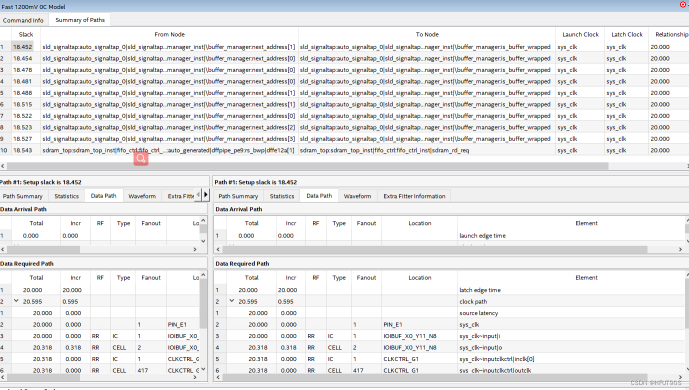

(6)就可以查看具体的时序报告了

总结

STA 笔面的关键点集中在以下几点:

(1)亚稳态

(2)建立时间和保持时间

(3)建立和保持检查(两个关键公式)

(4)STA工具和脚本语言

评论(0)

您还未登录,请登录后发表或查看评论