触发器,英文名称 flip-flop,简称FF,是具有记忆一位二进制代码的记忆单元,因此它的输出具有两个稳定状态——状态0和状态1。触发器有很多类型,如RS触发器、D触发器、JK触发器、T触发器等。

- 基本RS触发器

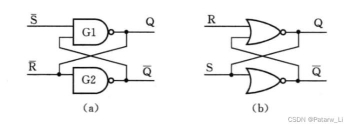

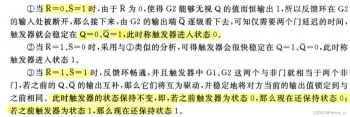

基本RS触发器是触发器中最基础的一种,可以由两个与非门或者两个或非门组成,电路图如下:

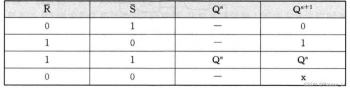

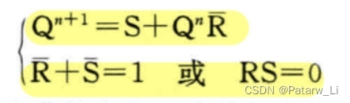

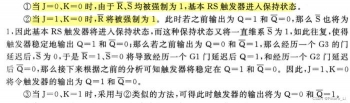

综上所述,RS触发器的真值表如下:

其卡诺图如下:

- 同步RS触发器

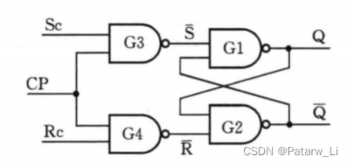

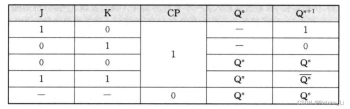

许多时候,我们希望触发器在只有在时钟来临的时候才改变其输出状态,其他时候,触发器维持,因为这样做可以让多个电路单元的状态同时得以改变,这个时钟,我们称为同步时钟,所以同步RS触发器也叫钟控RS触发器。同步RS触发器的电路图如下:

可以看到在原来R和S信号的前面增加了两个与非门。当时钟信号CP为0的时候,R和S全都为1,触发器会维持原来的状态;当时钟信号CP为1的时候,R和S即为Rc和Sc的值,此时触发器才工作。

综上所述,可以得到同步RS触发器的真值表如下:

需要注意的是,当CP有效时,若Rc、Sc发生了多次变化,触发器的输出和状态也会发生多次变化。在一个时钟周期中,触发器的输出发生多次变化的现象被称为空翻,这种现象是不希望发生的。

- 同步D触发器

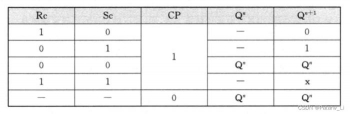

由于RS触发器的Rc和Sc不能同时为1,所以为了避免这种情况的发生,将Rc和Sc两个输入端合并为D输入端,从而有效地避免了两个输入端同时有效的情况,电路原理图如下:

其真值表如下:

需要注意的,同步D触发器同样存在空翻现象。

由于其高电平导通、低电平保持的特性,钟控D触发器还被称为 D锁存器。

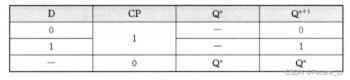

- 同步JK触发器

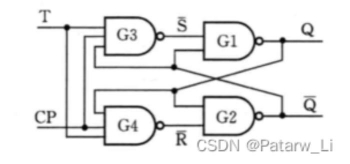

同步JK触发器是另一种有效避免基本RS触发器RS两端同时有效的电路结构,它也是在同步RS触发器的基础上进行简单修改得到的,电路如下

当CP为1的时候其工作情况如下:

其真值表如下,可见J=1、K=1时候会发生空翻现象:

T触发器

将同步与=JK触发器的JK两个输入连到一起,就得到了同步T触发器,电路如下:

真值表如下:

同步T触发器就相当于一个仅具有保持和翻转功能的同步JK触发器,存在空翻现象。

- 主从RS触发器

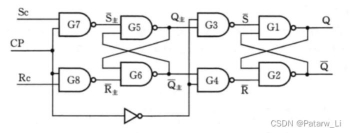

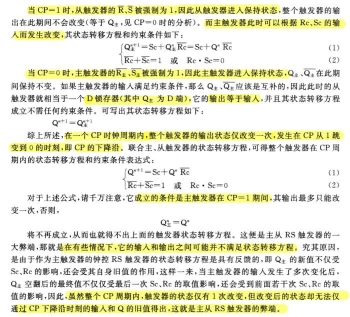

钟控触发器虽然可以对触发器的状态起到一定的控制作用,但是当CP有效时存在空翻的问题,为了让触发器的状态在CP有效期间仅改变一次,可以为触发器添加触发引导电路,形成主从结构的触发器,主从RS触发器的电路如下:

由上图可知,主从RS触发器实际上就是由两个钟控RS触发器级联组成的,其中G5、G6、G7、G8构成了主触发器,它的输入就是整个触发器的输入,它的输出是从触发器的输入;G1、G2、G3、G4构成了从触发器,它的输出就是整个触发器的输出。 下面是RS工作状况的分析:

可以看到,CP=1时,Rc和Sc有约束条件不能同时为1,在此期间改变Rc和Sc可以随意改变,Q主随着输入的改变而改变,但是由于从触发器的R¯

�

¯

和S¯

�

¯

被强制保持不变,所以在此期间真正的输出Q不会发生变化,也就避免了空翻效应;CP=0时,主触发器保持,从触发器直接输出Q主的内容,因为Q主不会发生变化,所以只会改变一次,在CP的下降沿时刻改变。

-

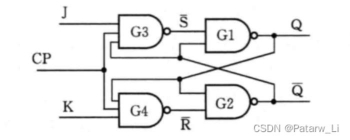

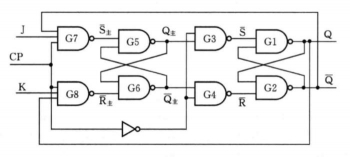

主从JK触发器

JK触发器存在由输出直接到输入的反馈,可以有效避免空翻、多次反转,且状态转移方程的成立不需要约束条件。原理电路如下:

-

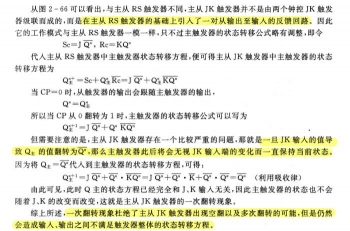

主从D触发器

主从RS触发器与主从JK触发器之所以会出现输入、输出之间不满足状态转移方程的情况,归根结底还是由于它们主触发器的状态转移方程中存在着反馈,即Q主的新值不完全受输入的控制,还会收到Q主旧值的影响。

因为钟控D触发器的输出完全由输入决定,所以采用钟控D触发器的级联所得到的主从D触发器,可以解决输入、输出之间不满足状态转移方程的问题。原理电路如下:

评论(0)

您还未登录,请登录后发表或查看评论