一、什么是时钟信号

时钟信号(Clock Signal)是时序逻辑的基础,用于决定逻辑单元中的状态何时更新,是有固定周期并与运行无关的信号量。时钟信号有固定的时钟频率,时钟频率是时钟周期的倒数。它有只有两个电平,一是低电平,另一个是高电平。高电平可以根据电路的要求而不同,例如 TTL 标准的高电平是 5V。最常见的时钟信号的占空比为 50%,也就是说,高电平和低电平的持续时间是一样的。

STM32F103C8T6的时钟信号由外部晶振(或单片机内部RC震荡电路)产生,它能够提供非常稳定和精确的频率。一般情况下我们都应该采用外部时钟,因为外部时钟比内部时钟要更稳定更准确。

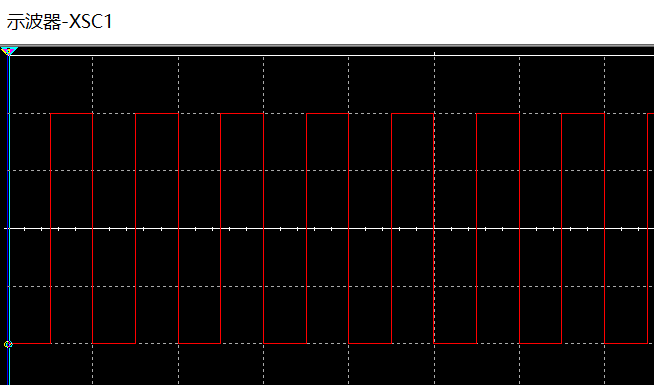

下图是在示波器中观测到的时钟信号:

二、时钟信号有什么用,单片机为什么需要时钟信号

我们可以直接百度一下,各种回答千奇百怪,但总结一下是以下几种:

-

同步操作:单片机内部由成千上万的小电路组成,包括逻辑门、寄存器、计数器等。所有这些电路都需要在严格的时间顺序下工作。时钟信号为这些电路提供了一个同步的节拍,以确保它们正确无误地协同工作。

-

指令执行:单片机的每条指令执行都需要一定数量的时钟周期来完成。时钟信号确定了指令的执行速度和整个程序的运行速度。

-

数据传输:在单片机与外部设备或其他微处理器通信时,时钟信号用于确保数据在正确的时间点被发送和接收。

-

定时与计时功能:时钟信号还用于实现各种定时和计时功能,比如产生延时、测量时间间隔等。

-

外设控制:一些外设可能需要在特定的时钟速率下工作,如串行通信接口(UART, SPI, I2C等),通过时钟信号可以保证数据流的正确性和可靠性。

-

功耗管理:在一些低功耗应用中,可以通过调整时钟频率来控制单片机的功耗,从而在保持性能的同时减少能量消耗。

-

系统稳定性:时钟信号的稳定性直接影响到单片机系统的可靠性。如果时钟信号不稳定,可能会导致系统运行错误或不可预期的行为。

是不是总有一下雾里看花终隔一层的感觉?

我们可以尝试从单片机的底层来分析这个问题,单片机内部需要储存器、累加器、锁存器,这些都需要逻辑门电路。

插播:

储存器是一种电子设备或介质,用于存储数据和指令。在计算机架构中,它通常指的是可以读写的随机存取存储器(RAM)或只读存储器(ROM)。储存器可以暂时或永久保存信息,并且可以是易失性的(断电后信息丢失,如DRAM)或非易失性的(断电后信息仍然保留,如Flash存储器)。

累加器通常是中央处理单元(CPU)内的一个特殊寄存器,用于在执行算术和逻辑运算时暂存结果。在许多处理器设计中,累加器是算术逻辑单元(ALU)的主要工作区域,用于“累加”结果,即它会保存前一计算的结果,并将其与下一步的操作数结合进行新的运算。

锁存器是一种基本的存储电路,它可以存储一位二进制信息(0或1)。锁存器的一个关键特性是它具有两个稳定状态,可以在输入信号的控制下从一个状态切换到另一个状态,并在输入信号消失后保持当前状态。D型触发器是一种常见的锁存器,它在时钟信号的特定边沿(上升沿或下降沿)捕获输入信号,并将其锁存直到下一个时钟边沿。

D型触发器(D Flip-Flop)是一种数字电子电路,用于存储一位(bit)的信息,是时序逻辑电路的基本构件。它命名中的“D”代表“Data”,指的是数据输入端。D型触发器的工作原理是在时钟信号的特定边沿(通常是上升沿),D输入端的值被捕获并传送到Q输出端。Q输出端的值将保持稳定,直到下一个时钟信号的边沿到来。这意味着D型触发器可以看作是一个具有延迟特性的单比特存储器。

锁存器就是一个D触发器,而触发器的置1、清0、置数的功能都需要跳变沿。而这个跳变沿就得有某个脉冲信号提供,答案已经呼之欲出,是时钟信号提供了这个跳变沿!STM单片机基本功能都得需要时钟信号这颗“心脏”的跳动才能正常工作!

从单片机对指令的执行来看,在对一个指令的执行中需要时钟信号来同步各个组件进行同步工作,比如寄存器、算术逻辑单元(ALU)、内存接口等在时钟信号的指挥下协同工作。

STM32F103是基于ARM Cortex-M3处理器核心的微控制器,由STMicroelectronics生产。Cortex-M3处理器是一款32位RISC核心, 在Cortex-M3处理器上,指令的时钟周期数可以根据指令类型和执行环境的不同而有很大差异。ARM Cortex-M3处理器采用的是三级流水线架构。在具有流水线结构的处理器中,指令在多个阶段中被处理,例如取指、译码、执行等。时钟信号确保流水线的每个阶段在适当的时间进行,以免发生数据冲突或时间上的错误。再者说数据在组件之间的传输,也是在时钟信号的控制下进行的。例如,数据在内部总线上的转移、寄存器间的数据交换、内存读写操作等,都是在特定的时钟边沿发生的。

还有稳定状态和设置时间:

时钟信号的上升沿或下降沿可以定义数据稳定的时间点。组件必须在时钟信号的下一次跳变之前将数据稳定在输入引脚上(设置时间)并保持稳定一段时间(保持时间)。

插播:

在数字电路中,尤其是同步电路,稳定状态、设置时间(Setup Time)和保持时间(Hold Time)是确保正确时序的关键概念。让我们分别来解释它们:

稳定状态指的是数据信号在输入到一个触发器(如D触发器,常用于寄存器)时,保持不变的状态。为了正确地被捕获,数据信号需要在时钟信号的特定边沿(通常是上升沿或下降沿)之前和之后保持稳定。

设置时间是指在时钟信号的捕获边沿(如上升沿)到来之前,数据必须稳定并准备好被捕获的最小时间。在这段时间内,数据线上的信号不能改变;如果数据在这段时间内发生变化,那么触发器可能无法正确地捕获数据,导致不确定的输出状态。设置时间是由电路设计者根据电路的特性设定的,它确保数据能够在时钟边沿到来之前被稳定地读取。

保持时间是指在时钟信号的捕获边沿之后,数据必须保持稳定的最小时间。即使时钟信号已经触发,数据也需要保持不变一段时间,以确保数据被可靠地捕获。如果数据在保持时间内改变,同样会导致触发器输出不确定的状态。

下面是一个简化的示例来说明这两个概念:

+---+ +---+ +---+

Clock | | | | | |

--------+ +-------+ +-------+ +-------

<-T-> <-T-> <-T->

| Setup |H| Hold |

Data --------+ | +----------------

\_/

Capture Edge

在这个示例中:

T代表时钟周期。Setup是设置时间,指数据在捕获边沿之前必须稳定的时间。Hold是保持时间,指数据在捕获边沿之后必须稳定的时间。Capture Edge是指捕获数据的时钟边沿。

另附一张F103时钟树图

三、外部时钟电路设计

先看电路图:

电路分为两部分:“高速时钟、低速时钟”

为啥要用俩时钟?还一个快一点,一个慢一点,这样不会干扰上面说了一大堆的同步吗?

先说一下为什么用俩时钟:

单片机(Microcontroller Unit,MCU)通常需要不同速率的时钟源以满足不同的系统要求。这些要求包括处理能力、功耗控制和外围设备的时钟需求。以下是一些使用高速时钟和低速时钟的原因:

高速时钟

-

提升性能:

- 高速时钟允许MCU以更快的频率运行,从而提高处理速度和响应时间,这对于需要快速处理大量数据或必须快速响应外部事件的应用至关重要。

-

外设支持:

- 某些外设,如USB接口、以太网控制器或高速ADC(模数转换器),可能需要高速时钟以保证它们能够以足够的速率运行。

-

数据吞吐量:

- 高速时钟能够提供更高的数据吞吐量,对于数据密集型任务,如图像处理或数据采集等,这是必须的。

低速时钟

-

节能:

- 低速时钟使得MCU能够在较低的频率下运行,从而显著减少功耗。这对于电池供电的设备非常重要,如可穿戴设备或远程传感器,因为它们需要尽可能长的电池寿命。

-

降低噪声:

- 在低速时钟下运行可以减少电磁干扰(EMI)和信号噪声,这对于某些需要高精度模拟读数的应用来说是有益的。

-

外围设备需求:

- 一些外围设备,如实时时钟(RTC)或低速串行通信接口(如I2C、SPI等),不需要高速时钟就能正常运行。使用低速时钟不仅可以节省能源,还能降低整个系统的复杂性。

-

动态性能调整:

- 动态时钟管理可以根据MCU的工作负载来调整时钟频率,这样在任务不繁重时可以降低时钟频率,而在需要高性能时可以提高时钟频率。

不同的时钟是如何避免相互干扰的呢?

举个栗子

如果CPU需要从RTC获取时间数据,这个数据必须从低速时钟域安全地传输到高速时钟域。这是通过在数据线上设置同步器来实现的,通常是两级或三级D触发器,确保信号稳定并防止亚稳态。当单片机需要在两个时钟之间切换(比如从高功耗模式切换到低功耗模式)时,内部时钟管理逻辑会在数据传输暂停时进行切换,防止切换过程中的数据损坏。

电路分析

乍一看这个电路还是很简单的,由一个晶振和两个串联在一起的电容并联组成。

但是我们为什么需要俩电容,又为什么需要这么连接呢?

(下文中的C2、C3指晶振两端的电容)

- 晶振在电气上可以等效为一个R1C1并联电路(称为动态电阻R1和电容C1),再串联一个电容C0的二端网络,这个网络有两个谐振点,其中较低的频率是串联谐振,较高的频率是并联谐振。

- 串联谐振:在串联谐振频率下,晶振的阻抗最小,晶振等效电路中的电感L和串联电容C0会与晶振内部的C1产生谐振。

- 并联谐振:在并联谐振频率下,晶振的阻抗最大,电路中的电感L会与外部并联的电容(比如上述电路中的C9和C12)产生谐振。

-

在这个极窄的频率范围内,晶振等效为一个电感L,与外部并联的电容(通常是两个电容C2和C3)组合,形成了一个并联LC谐振电路。这个并联谐振电路可以用于构建振荡器,因为它在特定的频率(即晶振的工作频率)上产生了谐振。

-

将晶振放入一个负反馈电路中,可以构建一个正弦波振荡器。负反馈有助于维持电路的稳定性,并且晶振的频率稳定性非常高,即使其他电路元件的参数发生变化,振荡器的频率也不会有很大变动。

-

在实际电路中,晶振的两端通常会分别连接电容C2和C3。这两个电容串联后的总电容量等于晶振的负载电容(指定的晶振工作所需的电容值)。通常,C2和C3的一个端点连接晶振,另一个端点接地。

-

通过选择与晶振的负载电容值相等的电容C2和C3,晶振电路能够达到预定的标称谐振频率。这是因为外部电容与晶振内部的电容C1一起决定了振荡频率。

电容的计算

C_e = 2 \times C_L - (C_s + C_i)

其中:

-

( C_e ) 是外接在晶振两端的每个电容的值。

-

( C_L ) 是晶振规格书中给出的容性负载值。

-

( C_s ) 为引线电容,可通过查询芯片数据手册获取。

-

( C_i )为引脚电容 可通过查询芯片数据手册获取,在3-6pF之间。

评论(0)

您还未登录,请登录后发表或查看评论